High efficient carrier phase synchronization for SDR using CORDIC implemented on an FPGA | Semantic Scholar

PDF) VHDL-based design and design methodology for reusable high performance direct digital requency synthesizers

PDF) VHDL-based design and design methodology for reusable high performance direct digital requency synthesizers

PDF) VHDL-based design and design methodology for reusable high performance direct digital requency synthesizers

Paperalrafeden-new - ttx - Design And Implementation of A Network on Chip Using FPGA Abstract - StuDocu

US7121639B2 - Data rate equalisation to account for relatively different printhead widths - Google Patents

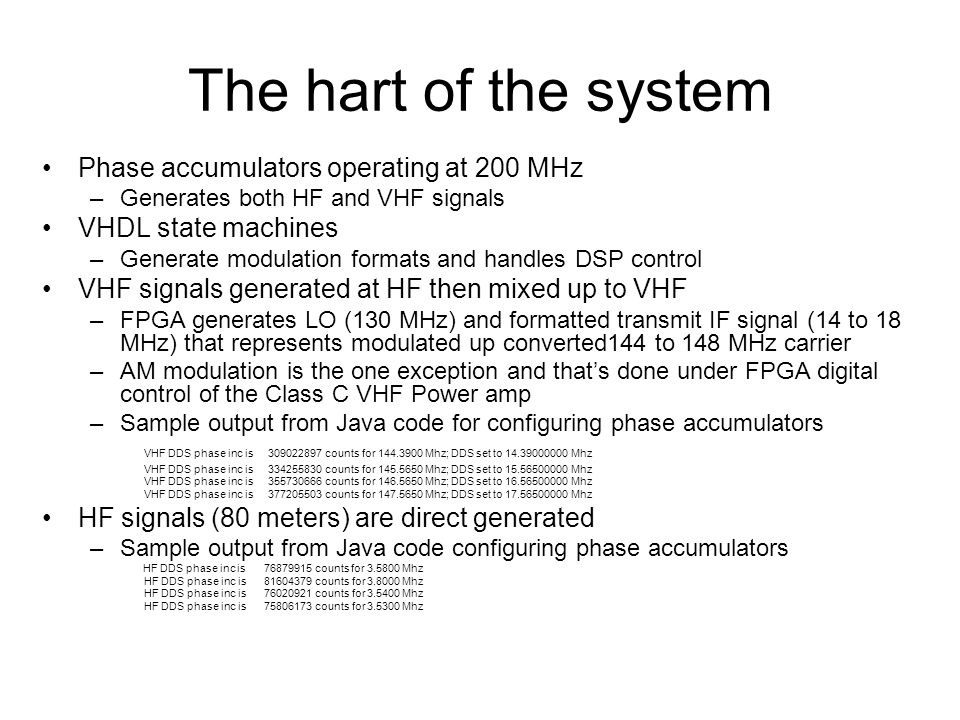

SDR TX Project Hardware / Software Update Jerry Boyd, WB8WFK (Hardware and FPGA VHDL ) Mike Pendley, K5ATM (PIC Software) October ppt download

Structured logic desing with VHDL-Skripta-Racunarski VLSI sistemi-Racunarska tehnika i informatika Part1 | Rezime' predlog Računarski sistemi - Docsity

Amazon.com: Gratico Kitchen Towels, Premium Quality,100% Cotton Dish Towels,Mitered Corners,Ultra Soft (Size: 20X30 Inch), Red/Green/White Highly Absorbent Bar Towels & Tea Towels - (Set of 6) : Home & Kitchen

![Vhdl For Engineers - Kenneth L. Short.pdf [PDF|TXT] Vhdl For Engineers - Kenneth L. Short.pdf [PDF|TXT]](https://html.pdfcookie.com/02/2019/12/18/52e1xp4o35v8/bg3.jpg)

![Vhdl For Engineers - Kenneth L. Short.pdf [PDF|TXT] Vhdl For Engineers - Kenneth L. Short.pdf [PDF|TXT]](https://html.pdfcookie.com/02/2019/12/18/52e1xp4o35v8/bg1.jpg)